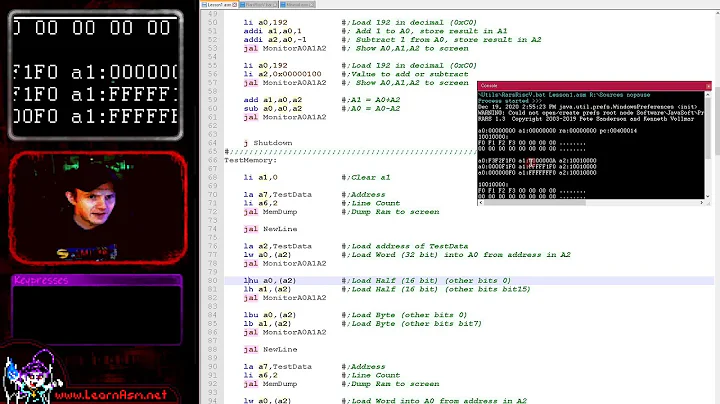

RISC-V assembly simulator

Solution 1

It sounds like you're looking for an instruction-level RISC-V simulator with an integrated front end that allows you to interactively edit machine code as well as view and manipulate the CPU state. I don't know of any tool for RISC-V that is as tightly integrated as MARS, but you can achieve a close approximation by combining some existing RISC-V tools, namely:

- An ISA simulator (Spike or QEMU)

- A RISC-V toolchain with assembler and compiler (RISC-V GNU toolchain)

- A debugger (gdb, included in the above toolchain)

- A debugger front end (gdb tui mode, DDD, gdbgui, or others)

I have had luck using QEMU + gdb or gdbgui as follows:

$ qemu-system-riscv32 -S -s -kernel /path/to/myprog.elf -nographic

Then in another console:

$ riscv64-unknown-elf-gdb /path/to/myprog.elf

(gdb) target remote localhost:1234

or

$ gdbgui -r -n -g /path/to/riscv64-unknown-elf-gdb /path/to/myprog.elf

NOTE: I notice that the gdb built under the riscv toolchain does not include support for tui mode by default.

NOTE2: QEMU is actually more than an ISA simulator -- it simulates various specific RISC-V target boards and their attendant peripherals.

Solution 2

Ripes : A graphical 5-stage RISC-V pipeline simulator & assembly editor

rv8 : RISC-V simulator for x86-64

risc-v-simulator : RISC-V assembler/simulator with GUI

RiscVAssemblerSuite : RISC V Assembler, Disassembler, and Simulation Environment

TinyEMU : TinyEMU is a system emulator for the RISC-V and x86 architectures

Solution 3

While using Spike and the RISC-V GNU toolchain certainly works and it is far from ideal for learning the ISA.

I actually spent a summer porting MARS for RISC-V because there wasn't a good option for beginners to use. RARS should be exactly what you are looking for.

A few things were removed from MARS for various reasons, but I do keep an eye on the repo so if there is an improvement missing, just make an issue.

Solution 4

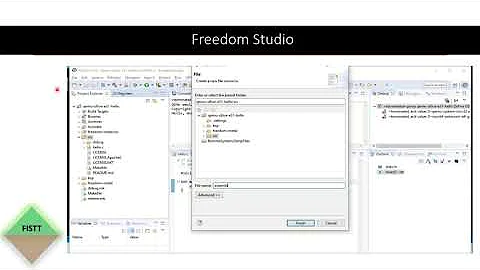

If you want a more high-level tool with a graphical interface, you can have a look at a small tool my university is using for teaching riscv. It comes with an inbuild assembler and simulator, which displays the content of all registers, memory and the state of a minimal riscv-pipeline for each cycle.

Unfortunatly the project is pretty old and the github-repo is not really up-to-date, but its still a convienient way to start with riscv.

https://github.com/unia-sik/riscVivid

Solution 5

Here is a great RISC-V simulator that was introduced in our computer organization class BRISC-V Simulator

Related videos on Youtube

hypergamer003

Updated on June 04, 2022Comments

-

hypergamer003 7 months

I'm trying to learn the RISC-V ISA. Is there a way to simulate RISC-V assembly code just like in MARS for the MIPS ISA?

-

James almost 4 yearsI just came across this web-based RISC-V simulator. Very simple and very easy to use: ascslab.org/research/briscv/emulator/emulator.html

-

-

JRN almost 3 yearsHow does it differ from the BRISC-V Emulator?

JRN almost 3 yearsHow does it differ from the BRISC-V Emulator?