VHDL alias syntax "<< ... >>"

12,540

A better solution than aliases to hierarchical signal references in packages: using a package to share signals between bfm-procedures and testbench toplevel. Example:

library ieee;

use ieee.std_logic_1164.all;

--VHDL 2008 with questasim

package bfm is

signal tb_ii_a : std_logic;

signal tb_ii_b : std_logic;

signal tb_oo_c : std_logic;

procedure wiggle;

end package;

package body bfm is

procedure wiggle;

begin

tb_oo_c <= force in '1';

wait for 10 ns;

tb_oo_c <= force in '0';

wait for 10 ns;

tb_oo_c <= force in tb_ii_a and tb_ii_b;

end procedure;

end package body;

library ieee;

use ieee.std_logic_1164.all;

use std.textio.all;

use std.env.all;

library work;

use work.bfm.all;

entity tb;

end tb;

architecture tb_dut1 of tb is

begin

dut : entity work.dut port map(

oo_a => tb_ii_a, -- output of dut input of tb bfm

oo_b => tb_ii_b, -- output of dut input of tb bfm

ii_c => tb_oo_c -- input of dut output of tb bfm

);

testcase : process

begin

wiggle;

wait for 100 ns;

std.env.stop(0);

end process;

end architecture;

Related videos on Youtube

Author by

Greg

Updated on September 11, 2022Comments

-

Greg over 1 year

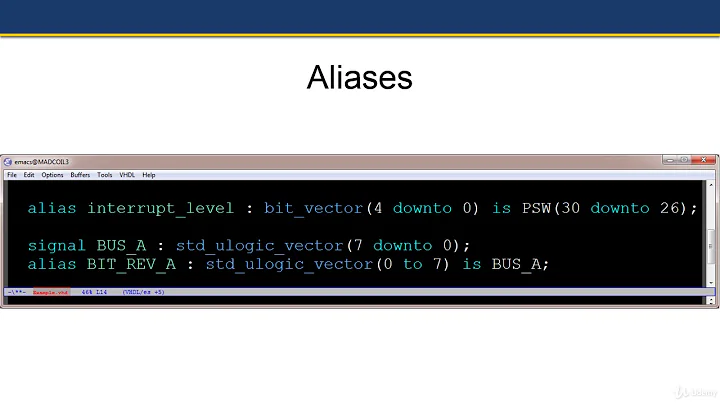

I'd like to understand the syntax used in the line of code below where an alternate name is created using an ALIAS declaration. Specifically, I'd like to know what the

<<and>>imply. An example alias statement is,alias x2_dac_data is << signal server.x2_dac_data : std_logic_vector(23 downto 0) >>;where

serveris an instantiated component andx2_dac_datais a signal with the component, but not listed in the port declaration.I've reviewed Pedroni's text and a course guide, neither of which reference the

<< ... >>syntax as it relates to alias.Thanks